論理回路

論理回路 verilog~BRAMと分散RAM~

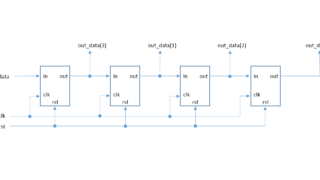

FIFOの設計をしていたときに学んだことをまとめておきます。 (※FIFOとは、First In First Outの略で最初に来たものを最初に出力するということ、論理回路以外でも様々な場面で使われる言葉)BRAMと分散RAMどっちを使...

論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路  論理回路

論理回路